Итак, не добившись результата с сабжевой платой я вернул ее заказчику. Однако, полученные результаты измерений не давали покоя и я решил подключить логический анализатор к заведомо исправной плате. В качестве подопытного была взята плата на базе ЮМ ICH9M от ноутбука Acer Apire 6930G (Quanta ZK2). Организация блоков ЮМ, мультиконтроллера и Flash памяти на этой плате такие же, как и на ZE7, поэтому она вполне подошла для исследования.

На работоспособном примере я выяснил, что считывание микопрограммы происходит только при наличии тактового сигнала и при деактивированных сигналах RSMRST# и PLTRST#. Во время исследования платы Acer AOD270 попытка передачи данных происходила без тактового сигнала (

), а в цепи PLTRST# был активный уровень. Это может свидетельствовать о неисправности ИМС системной логики (при условии отсутствия обрывов в других цепях).

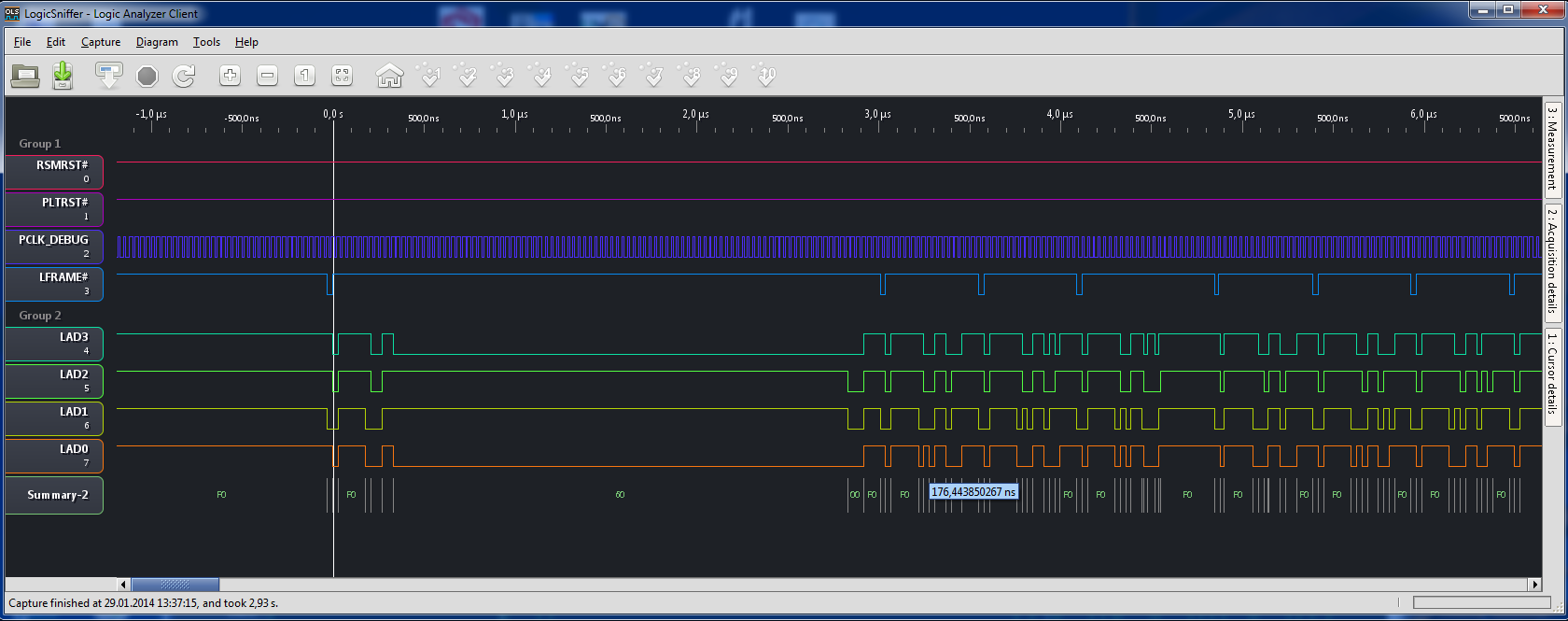

Ниже на рисунке представлен начальный обмен данными между ICH9M и мультиконтроллером.

Описание протокола передачи данных можно прочитать в документации в свободном доступе (см. ссылку в предыдущем посте). Дам некотоые краткие пояснения.

Передача данных производится кадрами. Начало кадра обозначается установкой цепи LFRAME# (активный низкий уровень). Цепью LFRAME# управляет хост-контроллер и это всегда системная логика. Мультиконтроллер всегда выступает в роли периферийного устройства. Защелкивание данных производится по фронту тактового сигнала.

Диаграмма к сожалению слишком сжата по оси x, т.к. хотел привести более наглядный пример, но разобраться в ней при желании можно. Видно, что каждый кадр начинается с активации линии LFRAME# и содержит поле START с кодом 0xD (0b1101), который соответствует команде Firmware Memory Read. Длина поля START равна одному такту. Далее следует поле IDSEL (Device Select): один такт и значение 0x0. Поле MADDR (Memory address) следует за полем IDSEL и длится семь тактов: в первом кадре передается адрес 0xFFFFFB0. Затем следует поле MSIZE (Memory size): один такт и значение 0x0, соответствующее считыванию одного байта. Следом наблюдаются поля TAR (Turn Around) - передача управления шиной LAD[3:0] периферийному устройству (2 такта) - и много тактов синхронизации (значение поля SYNC - 0x6), очевидно мультиконтроллер подготавливает данные к отправке. Когда данные готовы, мультиконтроллер устанавливает на шину данных значение 0x0 (это по прежнему поле SYNC), а следом данные из ячейки памяти (2 такта) - 0x00. Затем снова следует поле TAR для возврата управления шиной данных хост-контроллеру и завершение кадра.

В следующем кадре хост-контроллер запрашивает данные по адресу 0xFFFFFB1 и получает от мультиконтроллера значение 0x66 уже без задержки. И так далее.

Процес обмена происходит с чатотой тактового сигнала 33МГц и просматривается осциллографом с полосой 50МГц. LPC POST-карта эти данные не отображает, посокльку игнорирует кадры со значением поля START, соответствующим чтению/записи микропрограммы. При измерениях на плате ZE7, по данным ПО логического анализатора, в цепи LFRAME# наблюдалась частота 50МГц и сигнал такой частоты на дешевом осциллографе не удавалось пронаблюдать (вероятно не успевал сработать триггер).